# Exploiting Memristive BiFeO<sub>3</sub> Bilayer Structures for Compact Sequential Logics

Tiangui You,\* Yao Shuai, Wenbo Luo, Nan Du, Danilo Bürger, Ilona Skorupa, René Hübner, Stephan Henker, Christian Mayr, René Schüffny, Thomas Mikolajick, Oliver G. Schmidt, and Heidemarie Schmidt

Resistive switching devices are considered as one of the most promising candidates for the next generation memories and nonvolatile logic applications. In this paper, BiFeO<sub>3</sub>:Ti/BiFeO<sub>3</sub> (BFTO/BFO) bilayer structures with optimized BFTO/BFO thickness ratio which show symmetric, bipolar, and nonvolatile resistive switching with good retention and endurance performance, are presented. The resistive switching mechanism is understood by a model of flexible top and bottom Schottky-like barrier heights in the BFTO/BFO bilayer structures. The resistive switching at both positive and negative bias make it possible to use both polarities of reading bias to simultaneously program and store all 16 Boolean logic functions into a single cell of a BFTO/BFO bilayer structure in three logic cycles.

1. Introduction

Nonvolatile reconfigurable logic will allow researchers to develop compact, low-power devices and systems approaching brain-like intelligence. [1–5] The new hardware for basic logic computing should be integratable into silicon technology, and possess well defined state variables in large scale applications and low power consumption. It is well known that resistive switching devices can be integrated into large arrays for use as nonvolatile memory, analog or digital logics, sensors, and other applications that use resistance instead of voltage or charge as the physical state variable. [6,7]

Memristors are two-terminal passive devices which have been predicted theoretically as the fourth basic circuit element by L. O. Chua in 1971.[8] It was only in 2008 that the researchers from Hewlett-Packard Laboratories<sup>[9,10]</sup> revealed the missing link between resistive switching and memristors. In addition to being used in the next generation nonvolatile memories, the memristor is also a promising candidate to extend Moore's law beyond physical limits and implement beyond von-Neumann computing because only one memristor is needed to compute and store basic logic functions simultaneously in comparison to conventional CMOS (complementary metal-oxide-semiconductor) logic circuits that generally need much more components to realize

the basic logic functions<sup>[3,7]</sup> and physically separate processing and memory operations.<sup>[11]</sup> There have been many reports on the realization of Boolean logic functions with bipolar resistive switches (BRS) and with complementary resistive switches (CRS).<sup>[12-21]</sup> However, so far not all 16 Boolean logic functions could be realized with a single BRS or CRS. In 2009, J. J. Yang et al.<sup>[4]</sup> proposed a family of memristively switched reconfigurable devices which exhibit transitions between pairs of four current-transport end-states, namely shunted rectifier, forward rectifier, reverse rectifier and head-to-head rectifier, by strictly controlling the initial distribution of oxygen vacancies in the TiO<sub>2</sub> layer, and predicted that these unique devices may allow new nanoelectronic architectures in the fields of memory, logic,

T. You, N. Du, Dr. D. Bürger, I. Skorupa, Prof. O. G. Schmidt, Dr. H. Schmidt

Material Systems for Nanoelectronics

Chemnitz University of Technology

Chemnitz 09126, Germany

E-mail: tiangui.you@s2012.tu-chemnitz.de

Dr. Y. Shuai, Dr. W. Luo

State Key Laboratory of Electronic Thin Films and Integrated Devices

University of Electronic Science and Technology of China

Chengdu 610054, China

Dr. D. Bürger, I. Skorupa, Dr. R. Hübner Institute of Ion Beam Physics and Materials Research Helmholtz-Zentrum Dresden-Rossendorf Dresden 01314, Germany

DOI: 10.1002/adfm.201303365

Dr. S. Henker, Dr. C. Mayr, Prof. R. Schüffny Faculty of Electrical Engineering and Information Technology Institute of Circuits and Systems Technische Universität Dresden Dresden 01062, Germany Prof. T. Mikolajick NaMLab gGmbH Dresden 01187, Germany Prof. O. G. Schmidt Institute for Integrative Nanosciences IFW Dresden Dresden 01069, Germany

www.MaterialsViews.com

and synaptic computing. However, the reproducibility of the experimental current-voltage data is poor (Figure 3 in another work),[4] and the related devices were found to switch ON and OFF at low voltage bias with longer time constants<sup>[10]</sup> which may cause the resistive switching degradation by reading bias, so it is doubted whether the reported TiO2 devices are stable enough for the applications in universal memories or in nonvolatile Boolean function computing devices which require high retention and endurance performance. Here, we propose to form a BiFeO3:Ti/BiFeO3 (BFTO/BFO) bilayer structure which shows typical nonvolatile bipolar resistive switching and new symmetric bipolar resistive switching by tuning the thickness of the BFTO layer without electroforming process. The using of both positive and negative reading bias in one resistive switching device is first reported, which makes it feasible to realize all 16 Boolean logic functions with a single symmetric bipolar resistive switching bilayer structure in three logic cycles. With a write-back step in the third logic cycle, the nonvolatile logic can be configured.

#### 2. Results and Discussion

# 2.1. Fabrication and Electrical Characterization of BFTO/BFO Bilayer Structures

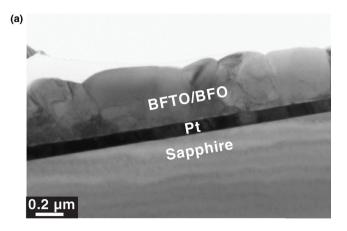

BFTO/BFO bilayer structures with different BFTO layer thicknesses have been fabricated on Pt/Sapphire substrates by pulsed laser deposition with sputtered circular Au contacts on top. The nominal thickness of BFO layer is 500 nm. The samples are labelled according to the nominal BFTO thickness of 50 nm, 100 nm, and 150 nm as sample-50, sample-100 and sample-150. The thickness and area of the Au top contacts are 30 nm and 0.045 mm<sup>2</sup>, respectively. Figure 1a shows a typical cross-sectional bright-field TEM image of sample-100. There is no visible interface between BFTO and BFO at a distance of ca. 100 nm from the Pt bottom contact, which is likely due to the same lattice structure and similar lattice parameters for BFTO and BFO, and the potential diffusion of Ti which might occur to the surface of the BFTO layer in the negative temperature gradient during its preparation.<sup>[22]</sup> Applying energy-dispersive X-ray spectroscopy with a conventional Si(Li) detector in scanning TEM mode, Ti could be detected by area analysis neither above the Pt layer in the ≈100 nm thick BFTO region nor in the ≈600 nm thick BFTO/BFO range (not shown). This may be due to the low Ti content of nominal 1 at% in BFTO and to the substitutional incorporation of Ti into the BFTO lattice without Ti cluster formation.<sup>[23]</sup> There are some grain boundaries passing through the entire BFTO/BFO bilayer structure. These grain boundaries may trap oxygen vacancies and form conductive channels inside the BFTO/BFO film, which may provide a path for leakage current between BFTO and BFO layer.[10,24] Therefore, it is supposed that there is no electron barrier forming at the interface between BFTO and BFO. Figure 1b depicts a schematic sketch of the BFO/BFTO bilayer structures and the electric measurement configuration, which indicates that the electric measurements are carried out by a sourcemeter device and the bias voltage is applied between the

**Figure 1.** a) Cross-sectional bright-field TEM image of the as-prepared BFTO/BFO bilayer structure consisting of a nominal 100 nm thick BFTO layer on a 100 nm thick Pt layer on c-sapphire and a subsequently deposited BFO top layer with a nominal thickness of 500 nm. b) the schematic sketch of the BFTO/BFO bilayer structure and the electric measurement configuration.

Au top electrode (terminal T1) and the Pt bottom electrode (terminal T2). The Pt bottom electrode is grounded.

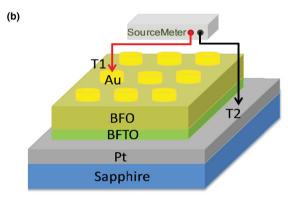

Figure 2a shows a sequence of ramping voltages, namely two positive triangular voltage sweeps followed by two negative triangular voltage sweeps. The voltage step is 0.4 V with the step time of 0.1 s. Figure 2b-d shows the current-voltage (I–V) curves of sample-50, sample-100, and sample-150, respectively. The numbers 1–16 label successive ramping voltages and the corresponding current branches in the I-V curves, and the arrows indicate the scanning direction of the applied ramping voltages. Sample-50 and sample-150 show typical bipolar resistive switching behavior without an electroforming step, in which the obvious hysteretic I-V behavior exists only for negative or positive ramping bias, respectively. However, in sample-100, the obvious hysteretic I–V behaviors exist in both negative and positive bias, which shows a symmetric bipolar resistive switching. After a positive writing bias the structure exhibits low resistive state in positive ramping bias (branch 2, 3, 4, 10, 11, and 12 in sample-100 and sample-150) and high resistance state only in the next negative ramping bias (branch 5 and 13 in sample-100 and sample-150), after a negative writing bias the structure shows low resistive state in negative ramping bias (branch 6, 7, 8, 14, 15, and 16 in sample-50 and sample-100)

www.MaterialsViews.com

www.afm-journal.de

Figure 2. a) Sequence of ramping voltages. The numbers 1–16 label successive ramping voltages and the corresponding current branches on a logarithmic scale of b) sample-50, c) sample-100, and d) sample-150.

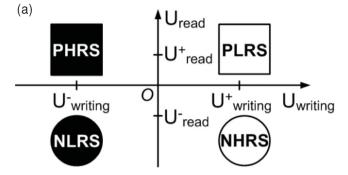

and high resistance state only in the next positive ramping bias (branch 1 and 9 in sample-50 and sample-100), which indicates the nonvolatility of the resistive switching. These I-V characteristics are quite stable as the I-V curves can be reproduced after 1 month (Supporting Information, Figure S1). The low resistance state and high resistance in positive ramping bias are abbreviated as PLRS and PHRS, respectively, [25] which are set and reset by positive writing bias and negative writing bias and read out by a positive reading bias. The low resistance state and high resistance in negative ramping bias are abbreviated as NLRS and NHRS, respectively, [25] which are set and reset by negative writing bias and positive writing bias and read out by a negative reading bias. The I-V curve of sample-100 suggests that both positive and negative reading bias can be used, and different resistance states can be obtained by different polarities of reading bias with the same writing bias.

# 2.2. Resistive Switching Mechanism in BFTO/BFO Bilayer Structures

In contrast to the abrupt current change with the formation and rupture of filaments, [26] here a rather gradually changing

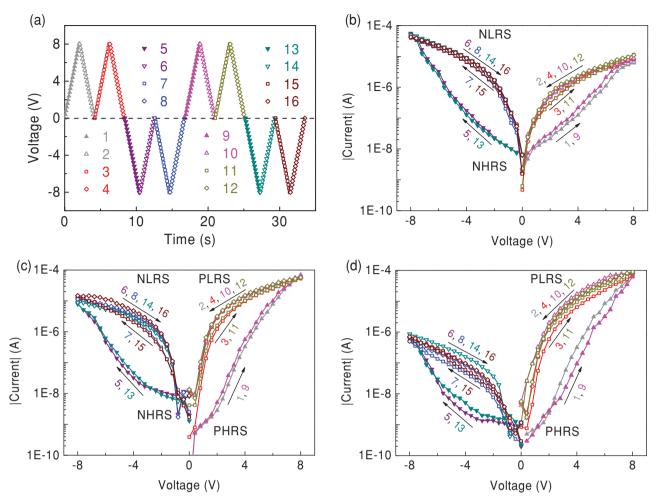

current is observed during resistive switching, which indicates the interface-mediated resistive switching in BFTO/BFO bilayer structures. The I-V characteristics with different Au contact area and the Au contact area dependent resistance value of different resistance states suggest that the resistive switching is induced by localized interface-mediated switching<sup>[26,27]</sup> (Supporting Information, Figure S2). In order to get further insight into the interface effect on the resistive switching, the *I–V* curves of sample-50, sample-100, and sample-150 in a small voltage range (from -2 V to +2 V) were measured in two different states, namely after applying a bias pulse of +8 V and after applying a bias pulse of -8 V for 0.1 s, which are shown in Figure 3a-c. The equivalent circuits corresponding to the bandstructure at different states are also presented in the right side of Figure 3 a-c. As shown in Figure 3a, the current of sample-50 is small in the both positive and negative voltage range after applying a positive bias pulse of +8 V, while a reverse rectification characteristic is observed after applying a bias pulse of -8 V. The equivalent circuit of sample-50 after applying a bias pulse of +8 V is a head-to-head rectifier which consists of two antiserially connected diodes ( $D_t$  and  $D_b$ ) due to the Schottky-like contact ( $\Phi_{\rm t}$  and  $\Phi_{\rm b}$ ) at both top (t) and bottom (b) interface and one resistor R<sub>i</sub> denoting the bulk resistance of the BFTO/BFO

www.MaterialsViews.com

Figure 3. I-V curves from -2 V to +2 V of a) sample-50, b) sample-100, and c) sample-150 measured after applying a writing bias of +8 V and -8 V. The schematic band alignment between the top (t) electrode on BFO and the bottom (b) electrode on BFTO and the corresponding barrier heights ( $\Phi_t$  and  $\Phi_b$ ), the distribution of the movable oxygen vacancies/ions (the black dots) and equivalent circuits are also indicated in the right side.

bilayer structure. The current is always blocked by one of the two Schottky-like interfaces regardless of the voltage polarity. After applying a pulse of -8 V, the Schottky-like barrier at the top interface decreases and the diode  $D_t$  turns into a resistor ( $R_t$ ) whereas  $D_b$  remains a Schottky-like diode. The current is controlled by  $D_b$  and shows a reverse rectification characteristic. By applying a negative reading bias,  $D_b$  is forward biased and a large current flows (NLRS). A reverse phenomenon is observed in sample-150. The current is small at both positive and negative voltage range after applying a bias pulse of -8 V due to the head-to-head rectifier ( $D_t$  and  $D_b$ ), and shows a forward rectifi-

cation characteristic after applying a bias pulse of +8 V, which suggests that the Schottky-like barrier at bottom interface decreases and the Schottky-like diode at top interface ( $D_t$ ) dominates the conductance. By applying a positive reading bias,  $D_t$  is forward and a large current flows (PLRS). While sample-100 demonstrates forward and reverse rectification characteristics after applying a bias pulse of +8 V and -8 V, respectively. This indicates the inversion between a reverse and a forward rectifier. After applying a pulse of +8 V, Schottky-like contact forms at top interface while Ohmic contact forms at bottom interface. The current is controlled by  $D_t$ . By applying a positive reading

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

www.MaterialsViews.com

bias,  $D_t$  is forward biased and a large current flows (PLRS); by applying a negative reading bias,  $D_t$  is reversed and a small current flows (NHRS). After applying a pulse of -8 V, Ohmic contact forms at top interface while Schottky-like contact forms at bottom interface. The current is controlled by  $D_b$ , by applying a positive reading bias,  $D_b$  is reversed and a small current flows (PHRS); by applying a negative reading bias,  $D_b$  is forward biased and a large current flows (NLRS).

These results suggest that a flexible Schottky-like barrier forms at top interface and Schottky-like barrier forms at bottom interface in sample-50, Schottky-like barrier forms at top interface and flexible Schottky-like barrier forms at bottom interface in sample-150, while flexible Schottky-like barrier forms at both top and bottom interface in sample-100, and the flexible Schottky-like barrier plays an important role in the resistive switching of BFTO/BFO bilayer structures. The flexible Schottky-like barrier may come from the migration of charged oxygen vacancies/ions under the electric field of writing bias<sup>[4,10,28]</sup> and the redistribution of carriers with ferroelectric switching.<sup>[29,30]</sup> However, the BFTO/BFO bilayer structures do not show significant ferroelectric switching under the writing bias (Supporting Information, Figure S3), so the flexible Schottky-like barrier of BFTO/BFO bilayer structures is supposed to result from the migration of charged oxygen vacancies/ions. The devices were also found to switch faster with larger writing bias (for example, 10 µs at 20 V). This is consistent with the fact that the drift velocity of vacancies increases in a larger electric field, [31,32] which further confirms that the flexible Schottky-like barrier comes from the migration of charged oxygen vacancies/ions. The black dots in the right side of Figure 2 indicate the distribution of the movable oxygen vacancies/ions under the certain writing bias. The accumulation of charged oxygen vacancies/ions in the interface effectively reduces the corresponding Schottky-like barrier as BFO can be regarded as n-type semiconductor due to the naturally produced oxygen vacancies,[33,34] while the Schottky-like barrier is recovered when the charged oxygen vacancies/ions drift away from the interface. It is reported that BFO with a small concentration of Ti doping exhibits higher resistivity than pure BFO.[35,36] In sample-50, the BFO layer possesses larger resistance due to the thin BFTO layer, so that most of the applied voltage drops across the BFO layer. The active region<sup>[4]</sup> is the top BFO layer which possesses flexible Schottky-like barrier. With the increase of BFTO thickness, the BFTO layer becomes more resistive and most of the applied voltage drops across the BFTO layer which results in the active region forming only in BFTO layer in sample-150. In sample-100, the resistance of BFO and BFTO is comparable, and both BFO and BFTO layers are active regions, so the flexible Schottky-like barrier forms at both top and bottom interface.

## 2.3. Nonvolatility of the Symmetric Bipolar Resistive Switching

In our previous work,<sup>[22,37–40]</sup> we have reported that a BFO single layer structures show typical bipolar resistive switching with excellent retention and endurance performance. In the following, we only present the nonvolatility of the symmetric bipolar resistive switching with sample-100.

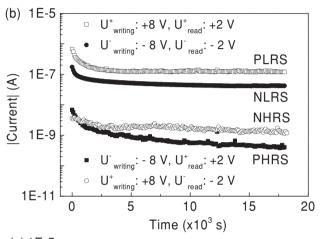

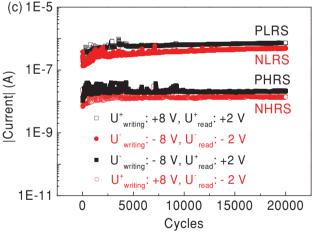

**Figure 4.** a) The relationship between the resistance states of sample-100 and the polarities of the applied writing bias  $U_{\rm writing}$  and the reading bias  $U_{\rm read}$ . b) Retention tests of sample-100 with positive and negative reading bias. The writing and reading bias for the four independent measurements are indicated in the legend. c) Endurance tests of sample-100 with the reading bias of +2 V (black curve) and -2 V (red curve).

Figure 4a reveals the relationship between the resistance state of sample-100 and the polarities of the applied writing and reading bias. If the writing and reading bias show the same polarity (both are positive or negative), the bilayer structure exhibits low resistance state (PLRS or NLRS), otherwise, the bilayer structure shows high resistance state (PHRS or NHRS). The resistance state of sample-100 is inverted by inverting

the polarity of the reading bias under the same writing bias. To check the nonvolatility of the states PLRS, PHRS, NLRS, and NHRS, retention tests were carried out by first applying a writing bias (+8 V or -8 V) and then repeating the reading bias (+2 V or -2 V) every 100 s. Generally, a current level detection is used as the resistance state detection for memristors and Figure 4b shows the current level detection results of PLRS, PHRS, NLRS, and NHRS. All PLRS, PHRS, NLRS, and NHRS show increasing resistance which may be caused by the redistribution of some charged oxygen vacancies/ions after the writing bias, however, PLRS and NLRS become stable after  $5 \times 10^3$  s and  $1 \times 10^4$  s, respectively. The low resistance state and high resistance state are still well defined after  $1.8 \times 10^4$  s. The endurance properties with the positive and negative reading bias were also examined by repeating set/read/reset/read process for more than  $2 \times 10^4$  cycles as shown in Figure 4c. The set/reset bias is +8 V or -8 V, and the reading bias is +2 V or -2 V. The PLRS, PHRS, NLRS, and NHRS in endurance tests show the same starting current values as for the retention tests and gradually increase until saturation due to Joule heating during the endurance tests. After  $1 \times 10^4$  cycles, the read currents become stable, and the memory window is well kept after switching for  $2 \times 10^4$  cycles. The low resistance state and high resistance state are distinguishable and it is expected that the stabilization and reliability of the resistance states can be further improved by Ar<sup>+</sup> irradiation.<sup>[38–40]</sup>

#### 2.4. Realization of All 16 Boolean Logic Functions

In recent years, a concept of sequential logic<sup>[7,12,21]</sup> has been introduced to realize the logic functions in a sequential operation with a small set of resistive switching devices. E. Linn et al.[21] showed that a single BRS or CRS with write-back step can be used to realize 14 of 16 Boolean logic functions (except XOR and XNOR) in at most three sequential logic cycles. Sample-50 and sample-150 with typical bipolar resistive switching can be used to realize the 14 Boolean logic functions with negative and positive reading bias respectively. For the first time, we show that all 16 Boolean logic functions can be realized in three logic cycles with a single symmetric bipolar resistive switching BFTO/BFO bilayer structure cell in which the reading process can be used as an additional logic cycle. Furthermore, all 16 Boolean logic operations can be started with a same logic cycle, which is very favorable for practical applications. As an example, in the following we will explain how the Boolean logic function XOR can be programmed and stored into one BFTO/BFO bilayer structure cell.

Writing bias is determined by the potential of terminal 1 (*T1*) and terminal 2 (T2) which depend on the logic variables p and q (1 for high potential and 0 for low potential). Note that when T1 and T2 are at the same potential (T1 = 0 and T2 = 0 OR T1 =1 and T2 = 1), no potential difference exists across the device, the state of the device is unchanged. As mentioned above, with the same writing bias the output is different by using different reading bias. Therefore, the output is defined by T1, T2, initial state of the device (S') and reading bias (r) which are deemed to be the input variables. For the output, we assign the low resistance states PLRS and NLRS as logic "1" and the high resistance

**Table 1.** 16 possible combinations for the four input variables (T1, T2, S', and r) and the corresponding output (Out). The equations indicate the relationships between output and the input variables.

| T1 | T2 | S' | r | Out | Equation                                                                       |

|----|----|----|---|-----|--------------------------------------------------------------------------------|

| 0  | 0  | 1  | 1 | "1" | $Out = (T1 + \overline{T2}) \cdot S' \cdot \overline{r}$                       |

| 1  | 0  | 1  | 1 | "1" |                                                                                |

| 0  | 1  | 1  | 1 | "0" |                                                                                |

| 1  | 1  | 1  | 1 | "1" |                                                                                |

|    |    |    |   |     |                                                                                |

| 0  | 0  | 1  | 0 | "0" |                                                                                |

| 1  | 0  | 1  | 0 | "0" |                                                                                |

| 0  | 1  | 1  | 0 | "1" | $Out = \left(\overline{T1} \cdot T2\right) \cdot S' \cdot \overline{r}$        |

| 1  | 1  | 1  | 0 | "0" |                                                                                |

|    |    |    |   |     |                                                                                |

| 0  | 0  | 0  | 1 | "0" |                                                                                |

| 1  | 0  | 0  | 1 | "1" |                                                                                |

| 0  | 1  | 0  | 1 | "0" | Out = $(T1 \cdot \overline{T2}) \cdot \overline{S'} \cdot r$                   |

| 1  | 1  | 0  | 1 | "0" |                                                                                |

|    |    |    |   |     |                                                                                |

| 0  | 0  | 0  | 0 | "1" |                                                                                |

| 1  | 0  | 0  | 0 | "0" |                                                                                |

| 0  | 1  | 0  | 0 | "1" | $Out = \left(\overline{T1} + T2\right) \cdot \overline{S'} \cdot \overline{r}$ |

| 1  | 1  | 0  | 0 | "1" |                                                                                |

| _  | _  | _  |   |     | <del></del>                                                                    |

states PHRS and NHRS as logic "0". Because the state of the device is either state {PLRS, NHRS} or state {PHRS, NLRS}, state {PLRS, NHRS} can be assigned to 1 and state {PHRS, NLRS} can be assigned to 0. Similarly, positive reading bias is assigned to 1 and negative reading bias is assigned to 0. In Table 1, 16 possible combinations for these four input variables (T1, T2, S', and r) and the corresponding output (Out) are listed, the relationship between output and input variables can be summarized by this equation:

Out =

$$(T1 + \overline{T2}) \cdot S' \cdot r + (\overline{T1} \cdot T2) \cdot S' \cdot \overline{r} + (T1 \cdot \overline{T2}) \cdot \overline{S}' \cdot r + (\overline{T1} + T2) \cdot \overline{S}' \cdot \overline{r}$$

(1)

In general, by initializing the initial state S' to 1 or 0 which can be easily realized by writing pulse (T1 = 1, T2 = 0) or (T1 = 1, T2 = 0)0, T2 = 1), respectively, Equation 1 can be reduced to:

Out =

$$(T1 + \overline{T2}) \cdot r + (\overline{T1} \cdot T2) \cdot \overline{r}$$

(2)

Out =

$$(T1 \cdot \overline{T2}) \cdot r + (\overline{T1} + T2) \cdot \overline{r}$$

(3)

Based on Equation 2, the Boolean logic function XOR can be implemented by (T1 = 0, T2 = q) with r = p as shown in Equation 4.

| (a)                                  |                             |   |    |       | 1) /1    | CI            | 11/2    | C.LV     | 7    |              |                          |          |     | 11/1        |          | 11/2    | C.LV    |                      |

|--------------------------------------|-----------------------------|---|----|-------|----------|---------------|---------|----------|------|--------------|--------------------------|----------|-----|-------------|----------|---------|---------|----------------------|

| (a)                                  | $p \oplus q$                |   | q  | C.HV1 |          | C.HV2         |         |          | 4    | $p \oplus q$ |                          | C.HV1    |     | C.HV2       |          |         |         |                      |

|                                      |                             |   | T1 | T2    | T1       | T2            | R       | 4        |      |              |                          | T1       | T2  | T1          | T2       | r       |         |                      |

|                                      | р                           | q | S  | 1     | 0        | 0             | q       | р        | 4    | р            | q                        | S        | 0   | 1           | 1        | q       | р       |                      |

|                                      | 0                           | 0 | 0  |       | NHRS}    |               |         | NHRS='0' |      | 0            | 0                        |          |     |             |          | NHRS}   |         |                      |

|                                      | 1                           | 0 | 1  |       | NHRS}    |               |         | PLRS='1' | 4    | 1            | 0                        |          |     |             |          | NHRS}   |         |                      |

|                                      | 0                           | 1 | 1  |       |          |               | , NLRS} | NLRS='1' |      | 0            | 1                        |          |     |             |          | , NLRS} |         |                      |

|                                      | 1 1 0 {PLRS, NHRS} {PHRS, N |   |    |       | , NLRS}  | PHRS='0'      |         | 1 1 0    |      |              | {PHRS, NLRS} {PHRS, NLRS |          |     | , NLRS}     | PHRS='0' |         |         |                      |

|                                      |                             |   |    | C.F   | IV1      | C.H           | IV2     | C.LV     |      |              |                          |          | C.I | HV1         | C.F      | HV2     | C.LV    | /                    |

| (b)                                  |                             |   |    | C     | .HV1     | C.I           | HV2     | C.LV     |      |              |                          |          | C.H | V1          | C.HV     | /2      | C.LV    |                      |

| ` '                                  | 8F<br>4-                    |   |    |       |          |               |         | Out='0'  |      |              |                          |          |     |             |          |         | Out='0' | 1E-5                 |

|                                      | 0 <del> </del> -4           |   |    |       |          |               |         |          |      |              |                          | $\dashv$ |     |             |          |         |         | 1E-7                 |

|                                      | -8 <u>-</u><br>8F           |   |    |       |          |               |         |          |      |              |                          |          |     |             |          |         |         | 1E-9                 |

|                                      | 4                           |   |    |       |          |               |         | Out='1'  |      |              |                          | Г        |     |             |          |         | Out='1' | 1E-5                 |

| 3                                    | 0<br>-4                     |   |    |       |          |               |         |          |      |              |                          | -        |     |             |          |         |         | 1E-7<br>1E-9<br>1E-5 |

| 12                                   | -8[                         |   |    |       |          |               |         |          | ]    |              |                          |          |     |             |          |         |         | 1E-9                 |

| V <sub>T1</sub> -V <sub>T2</sub> (V) | 8<br>4                      |   |    |       |          |               |         | Out='1'  |      |              |                          | _        |     |             |          |         | Out='1' | 1                    |

| >                                    | 0[-<br>-4                   |   |    |       |          |               |         |          |      |              |                          |          |     |             |          |         |         | 1E-7                 |

|                                      | -8                          |   |    |       |          |               |         |          |      |              |                          |          |     |             |          |         |         | ] <sub>1E-9</sub>    |

|                                      | 8F<br>4F                    |   |    |       |          |               |         | Out='0'  |      |              |                          |          |     |             |          |         | Out='0' | 1E-5                 |

|                                      | 0                           |   |    |       |          |               |         |          |      |              |                          |          |     |             |          |         |         | 1E-7                 |

|                                      | -4<br>-8                    |   |    | 1     |          |               |         |          | 1    |              |                          | - 1      |     |             |          |         |         | 1E-9<br>0.4          |

|                                      | 0.0                         |   |    | 0.1   | (<br>Tir | ).2<br>ne (s) | 0.      | 3 C      | .4 0 | .0           |                          | 0.       | 1   | 0.2<br>Time |          | 0.3     | (       | 0.4                  |

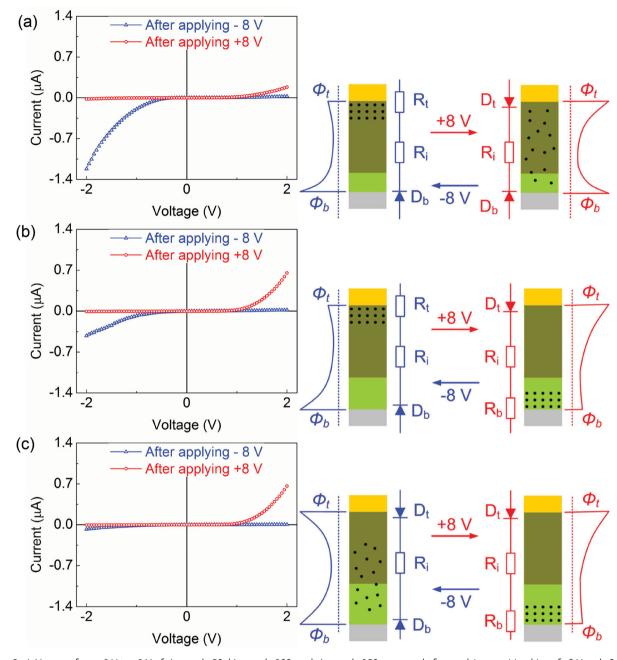

Figure 5. a) Logic operations for XOR with three logic cycles including two writing cycles C.HV1 and C.HV2 using  $\pm 8$  V and one read cycle C.LV using  $\pm 2$  V applied to the sample-100. b) The experimental demonstration of the sequential XOR for all four input states of p and q. The black and red curves display the applied potential between T1 and T2 ( $V_{T1}-V_{T2}$ ) on a linear scale and the absolute value of the measured current on a logarithmic scale, respectively. The red dashed line is the current threshold level for Out = "0" and Out = "1", and the black dotted line is the zero-bias of  $V_{T1}-V_{T2}$ .

XOR is also possible by (T1 = 1, T2 = q) with r = p based on Equation 3 as shown in Equation 5.

Out =

$$p \times QR = \overline{q} \cdot p + q \cdot \overline{p} = (0 + \overline{q}) \cdot p + (\overline{0} \cdot q) \cdot \overline{p}$$

(4)

Out =

$$p \text{ XOR } q = \overline{q} \cdot p + q \cdot \overline{p} = (1 \cdot \overline{q}) \cdot p + (\overline{1} + q) \cdot \overline{p}$$

(5)

**Figure 5**a shows the realization of XOR with three logic cycles C.HV1, C.HV2, and C.LV (two writing cycles C.HV1 and C.HV2 and one reading cycle C.LV) and the corresponding experimental demonstrations with the prepared bilayer structure are shown in Figure 5b. Contrary to nonvolatile logics, the reading bias in the third logic cycle C.LV depends on the logic variable p (or q for the other Boolean logic functions). To accommodate nonvolatile logics, a write-back step in the third logic cycle C.LV can be used to store the output of the logic operations in the same device and make the reading bias independent of the input logic variables, which is not shown in Figure 5. For example, a positive and negative writing bias is applied in the write-back step to store the output 1 and 0

of the logic operations into the same device, respectively, and then both output 1 and 0 can be non-destructively read out by positive reading bias until next logic operation. Note that the write-back step is only performed in the third logic cycle C.IV for nonvolatile logics.

The other 15 Boolean logic functions can also be realized with three logic cycles (Supporting Information, Figure S4). The first logic cycle C.HV1 of all 16 Boolean logic operations can be a positive writing pulse and can be also a negative writing pulse. The nonvolatile logics can be realized by a write-back step in the third logic cycle C.LV. It is important to note that the high substrate temperature during thin film growth, the unstructured bottom electrode and the large thickness of BFTO/BFO bilayer structures do not necessarily compete the benefits of CMOS compatibility. We suggest to overcome these challenges by heating the sample surface during thin film growth using laser heating instead of using resistive heating, by structuring both the bottom and the top electrodes and by introducing well defined shunts into unstructured BFTO/BFO bilayer structures using Ar<sup>+</sup> ion irradiation. [40] There are other promising reports

- Views

www.MaterialsViews.com

on hybridizing CMOS with unstructured resistive switching  ${\rm TiO_2~layers.}^{[3,41]}$  Therefore, we consider unstructured BFTO/BFO bilayer structures with structured bottom and top electrodes as prospective building blocks for new micro/nano-electronic systems, for example, beyond von-Neumann computers.

3. Conclusions

In summary, BFTO/BFO bilayer structures have been fabricated. The bilayer structure with optimized BFTO/BFO thickness ratio shows nonvolatile bipolar resistive switching and symmetric bipolar resistive switching characteristics under both positive and negative bias. The high stability and reliability of LRS and HRS in symmetric bipolar resistive switching with positive and negative reading bias are examined by retention and endurance tests. By using the reading process as an additional logic cycle, the resistance state of symmetric bipolar resistive switching is inverted by inverting the polarity of the reading bias under the same writing bias, which makes it feasible to program all 16 Boolean logic functions into a single cell of a BFTO/BFO bilayer structure in three logic cycles. Nonvolatile logic is realized by a write-back step in the third logic cycle which stores the output of the logic operation until next writing cycle in the same cell of a BFTO/BFO bilayer structure. In the future, the BFTO/BFO bilayer structures can be integrated into crossbar circuits to achieve different arithmetic operations from single or cascaded cells (logic gates).

## 4. Experimental Section

Fabrication of BFTO/BFO Bilayer Thin Film Structures: To obtain a BFTO/BFO bilayer structure, a BFTO film with nominal 1 at% Ti was first deposited on Pt/Sapphire substrate, and then an undoped BFO film was deposited on the BFTO film without breaking vacuum and substrate heating by pulsed laser deposition (PLD). Approximately 5 min have been used to rotate the BFO target to the sputter position and to stabilize the system. The laser energy, laser repetition rate, oxygen ambient pressure, and growth temperature are 2 J cm<sup>-2</sup>, 10 Hz, 13 mTorr, and 650 °C, respectively. The nominal thicknesses of BFTO layer are 50 nm, 100 nm, and 150 nm for sample-50, sample-100, and sample-150, respectively; and the thickness of BFO layer was kept at 500 nm. Following BFTO/BFO deposition, circular Au top contacts with an area of 0.045 mm² and a thickness of 30 nm were fabricated by DC magnetron sputtering at room temperature using metal shadow mask.

Characterization: Bright-field transmission electron microscopy (TEM) imaging as well as energy-dispersive X-ray spectroscopy (EDXS) in the scanning TEM mode was performed in cross-sectional geometry of sample-100 by means of an image-corrected FEI Titan 80–300 microscope. The current–voltage (*I–V*), the retention and endurance characteristic curves were measured by the two-probe method with a Keithley 2400 sourcemeter at room temperature under the dark condition.

### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### Acknowledgements

T.Y. acknowledges the China Scholarship Council (Grant Code: 201206970006) and the Initiative and Networking Fund of the Helmholtz

Association (Grant Code: VI MEMRIOX VH-VI-422), D.B. and H.S. acknowledge the Deutsche Forschungsgemeinschaft (grant number: BU 2956/1–1 and SCHM1663/4–1).

Received: September 30, 2013 Revised: December 6, 2013 Published online: February 24, 2014

- [1] E. M. Vogel, Nat. Nanotechnol. 2007, 2, 25.

- [2] M. Tanaka, S. Sugahara, IEEE Trans. Electron Devices 2007, 54, 961.

- [3] Q. Xia, W. Robinett, M. W. Cumbie, N. Banerjee, T. J. Cardinali, J. J. Yang, W. Wu, X. Li, W. M. Tong, D. B. Strukov, G. S. Snider, G. Medeiros-Ribeiro, R. S. Williams, *Nano Lett.* **2009**, *9*, 3640.

- [4] J. J. Yang, J. Borghetti, D. Murphy, D. Stewart, R. S. Williams, Adv. Mater. 2009, 21, 3754.

- [5] T. N. Theis, P. M. Solomon, Science 2010, 327, 1600.

- [6] P. J. Kuekes, D. R. Stewart, R. S. Williams, J. Appl. Phys. 2005, 97, 034301.

- [7] J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart, R. S. Williams, *Nature* **2010**, *464*, 873.

- [8] L. O. Chua, IEEE Trans. Circuit Theory 1971, 18, 507.

- [9] D. B. Strukov, G. S. Snider, D. R. Stewart, R. S. Williams, *Nature* 2008, 453, 80.

- [10] J. J. Yang, M. D. Pickett, X. Li, D. A. A. Ohlberg, D. R. Stewart, R. S. Williams, *Nat. Nanotechnol.* 2008, 3, 429.

- [11] C. D. Wright, P. Hosseini, J. A. V. Diosdado, Adv. Funct. Mater. 2013, 23, 2248.

- [12] E. Lehtonen, J. H. Poikonen, M. Laiho, Electron. Lett. 2010, 46, 239.

- [13] S. Yu, J. Liang, Y. Wu, H. P. Wong, Nanotechnology 2010, 21, 465202.

- [14] S. C. Puthentheradam, D. K. Schroder, M. N. Kozicki, Appl. Phys. A 2011, 102, 817.

- [15] Y. Chai, Y. Wu, K. Takei, H. Y. Chen, S. Yu, P. C. H. Chan, A. Javey, H. S. P. Wong, *IEEE Trans. Electron Devices* 2011, 58, 3933.

- [16] X. Liu, S. M. Sadaf, M. Son, J. Shin, J. Park, J. Lee, S. Park, H. Hwang, Nanotechnology 2011, 22, 475702.

- [17] R. S. Shenoy, K. Gopalakrishnan, B. Jackson, V. Kirwani, G. W. Burr, C. T. Rettner, A. Padilla, D. S. Bethune, R. M. Shelby, A. J. Kellock, M. Breitwisch, E. A. Joseph, R. Dasaka, R. S. King, K. Nguyen, A. N. Bowers, M. Jurich, A. M. Friz, T. Topuria, P. M. Rice, B. N. Kurdi, 2011 IEEE Symp. VLSI Technology, Tech. Dig. 2011, 94.

- [18] S. Tappertzhofen, E. Linn, L. Nielen, R. Rosezin, F. Lentz, R. Bruchhaus, I. Valov, U. Böttger, R. Waser, *Nanotechnology* 2011, 22, 395203.

- [19] M. J. Lee, C. B. Lee, D. Lee, S. R. Lee, M. Chang, J. H. Hur, Y. B. Kim, C. J. Kim, D. H. Seo, S. Seo, U. I. Chung, I. K. Yoo, K. Kim, Nat. Mater. 2011, 10, 625.

- [20] O. Kavehei, S. Al-Sarawi, K. R. Cho, K. Eshraghian, D. Abbott, IEEE Trans. Nanotechnol. 2012, 11, 374–385.

- [21] E. Linn, R. Rosezin, S. Tappertzhofen, U. Böttger, R. Waser, Nanotechnology 2012, 23, 305205.

- [22] Y. Shuai, X. Ou, W. Luo, A. Mücklich, D. Bürger, S. Zhou, C. Wu, Y. Chen, W. Zhang, M. Helm, T. Mikolajick, O. G. Schmidt, H. Schmidt, Sci. Rep. 2013, 3, 2208.

- [23] M. A. Neto, Q. Fan, E. Rereira, Diamond Related Mater. 2001, 10, 316.

- [24] G. Bersuker, P. Zeitzoff, G. Brown, H. R. Huff, *Mater. Today* 2004, 7, 26.

- [25] S. Balatti, S. Larentis, D. C. Gilmer, D. Lelmini, Adv. Mater. 2013, 25, 1474.

- [26] I. G. Baek, M. S. Lee, S. Seo, M. J. Lee, D. H. Seo, D.-S. Suh, J. C. Park, H. S. Kim, I. K. Yoo, U-In Chung, J. T. Moon, *IEDM Tech. Dig.* 2004, 587.

- [27] H. Sim, H. Choi, D. Lee, M. Chang, D. Choi, Y. Son, E.-H. Lee, W. Kim, Y. Park, I.-K. Yoo, H. Hwang, *IEDM Tech. Dig.* **2005**, 758.

ADVANCED FUNCTIONAL MATERIALS www.afm-journal.de

#### www.MaterialsViews.com

- [28] R. Meyer, L. Schloss, J. Brewer, R. Lambertson, W. Kinney, J. Sanchez, D. Rinerson, in *Proc. Non-Volatile Memory Technol.* Symp. 2008, 1.

- [29] C. Wang, K. Jin, Z. Xu, L. Wang, C. Ge, H. Lu, H. Guo, M. He, G. Yang, Appl. Phys. Lett. 2011, 98, 192901.

- [30] A. Q. Jiang, C. Wang, K. J. Jin, X. B. Liu, J. F. Scott, C. S. Hwang, T. A. Tang, H. B. Lu, G. Z. Yang, Adv. Mater. 2011, 23, 1277.

- [31] J. Blanc, D. L. Staebler, Phys. Rev. B 1971, 4, 3548.

- [32] D. B. Strukov, R. S. Williams, App. Phys. A 2009, 94, 515.

- [33] X. Y. Chen, T. Yu, F. Gao, H. T. Zhang, L. F. Liu, Y. M. Wang, Z. S. Li, Z. G. Zou, J. M. Liu, Appl. Phys. Lett. 2007, 91, 022114.

- [34] C. Ge, K. J. Jin, C. Wang, H. B. Lu, C. Wang, G. Z. Yang, Appl. Phys. Lett. 2011, 99, 063509.

- [35] N. M. Murari, R. Thomas, R. E. Melgarejo, S. P. Pavunny, R. S. Katiyar, J. Appl. Phys. 2009, 106, 014103.

- [36] Y. H. Gu, Y. Wang, F. Chen, H. L. W. Chan, W. P. Chen, J. Appl. Phys. 2010, 108, 094112.

- [37] Y. Shuai, S. Zhou, D. Bürger, M. Helm, H. Schmidt, J. Appl. Phys. 2011, 109, 124117.

- [38] Y. Shuai, N. Du, X. Ou, W. Luo, S. Zhou, O. G. Schmidt, H. Schmidt, Phys. Status Solidi C 2013, 10, 636.

- [39] Y. Shuai, X. Ou, W. Luo, N. Du, C. Wu, W. Zhang, D. Bürger, C. Mayr, R. Schüffny, S. Zhou, M. Helm, H. Schmidt, *IEEE Electron Device Lett.* 2013, 34, 54.

- [40] X. Ou, Y. Shuai, W. Luo, P. F. Siles, R. Kögler, J. Fiedler, H. Reuther, S. Zhou, R. Hübner, S. Facsko, M. Helm, T. Mikolajick, O. G. Schmidt, H. Schmidt, App. Mater. Interfaces DOI: 10.1021/ am404144c.

- [41] K.-T Cheng, D. B. Strukov, ACM Int. Symp. Phys. Design 2012, 33.